다중 쓰레드 프로그램의 경쟁상태오류 검출기법 분류

KAIST Provable SW 연구실 홍신, 김문주

Motivations

(1/2)

Many SW applications utilize multi-threaded programming techniques as multi-core hardware become widely spread.

- Writing correct multi-threaded programs is difficult.

- Exponential number of execution scenarios

- Detecting errors by assertion is not effective

- → Bug detection techniques specialized for concurrency errors

Motivations

(2/2)

- Many techniques have evolved

- Deadlock: [K. M. Chandy et al., TOCS 1983],[R. Agarwal et al., IBM J. 2010]

- However, for race bugs, techniques have used their own definitions and notations without any reliance on a common ground or platform.

|                 | Bug name                | Specification                         | Target program | Bug checking method                                                      |

|-----------------|-------------------------|---------------------------------------|----------------|--------------------------------------------------------------------------|

| Kivati          | Atomicity violation     | User annotations                      | C program      | Memory access pattern in run-time                                        |

| LiteRace        | Data race               | N/A                                   | x86 binary     | Execution orders in run-time                                             |

| Havelund et al. | High-level<br>data race | Analyze code and infer specifications | Java           | Relationship between synchronization and variables in run-time execution |

→ Develop <u>classification</u> which clarify the relationship between techniques and provide a clear top-down view of race detection techniques

Approach

(1/2)

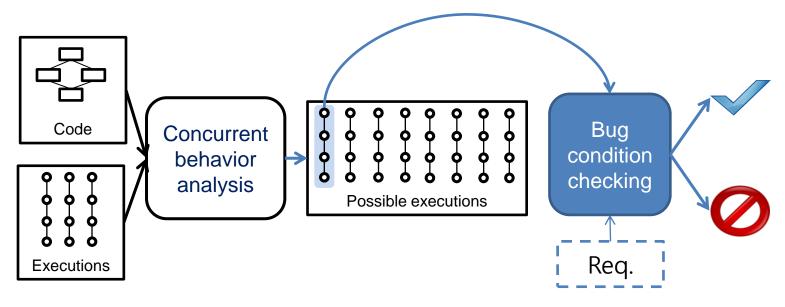

- Provide a <u>formal execution model</u> and specify various bug conditions according to the model

- Decoupling what to detect and how to detect

- Concurrent behavior analyses: generate potential executions of a program by information from static/dynamic analyses [F. Chen et al. ICSE 2008]

- Bug condition checking: examine a given execution is acceptable/erroneous

Classify bug conditions according to type of specifications

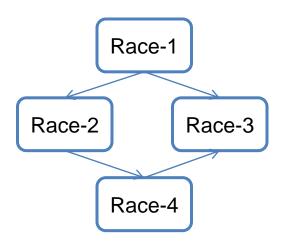

### Contents

- Execution model for multithreaded program

- Four classes of race detection techniques

- For each class,

- bug example

- bug conditions

- techniques for checking conditions

Implications for better race detections

## Execution Model

An execution model of a target program P used for technique D is defined as

$$EM_P(D) = (T, e, \triangleright, B_{op}, A_{data})$$

Program behavior Requirements

- T: a finite set of threads

- e: an interleaved execution a finite sequence of operations  $p_1, p_2, \dots, p_n$  where  $p_i \in Operation$

- $thread(p) \in T$

- $optr(p) \in Operator$ conflict(optr(p), optr(q)) if the operators of p and q are commutable.

- $oprd(p) \subseteq V_S$

# **Execution Model**

(2/5)

• An execution model of a target program P used for technique D is defined as

$$EM_P(D) = (T, e, \triangleright, B_{op}, A_{data})$$

- T: a finite set of threads

- $\pmb{e}$  : an interleaved execution a finite sequence of operations  $p_{\rm 1},\,p_{\rm 2},\,\dots$  ,  $p_n$  where  $p_i{\in}Operation$

- $thread(p) \in T$

- $optr(p) \in Operator$ conflict(optr(p), optr(q)) if the operators of p and q may not be commutable.

- $oprd(p) \subseteq V_S$

• An execution model of a target program P used for technique D is defined as

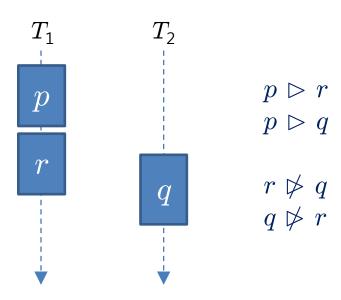

$$EM_P(D) = (T, e, \triangleright, B_{op}, A_{data})$$

- Operations in an execution are totally ordered by their start time.

- $\triangleright$   $\subseteq$  Operation imes Operation  $(p, q) \in \triangleright$  if  $t_s(p) < t_s(q)$  and  $t_e(p) < t_e(q)$

/ 33

An execution model of a target program P used for technique D is defined as

```

EM_P(D) = (T, e, \triangleright, B_{op}, A_{data})

B_{op} = \{b_1, b_2, ..., \} \text{ where } b_i : Operation \times Operation

An execution of an atomic code region corresponds to a sequence of operation, operation blocks. (p, q) \in b_i indicates that p and q are in the same operation block.

```

```

class BankAccount {

int balance ;

...

void withdraw(int amount) {

if (getBalance() >= amount) {

lock(m) ;

balance = balance - amount ;

unlock(m) ;

}

```

An execution model of a target program P used for technique D is defined as

$$EM_P(D) = (T, e, \triangleright, B_{op}, A_{data})$$

$A_{data}$ :  $V_S \times V_S$  where  $V_S$  is a set of shared variables

Frequently, variables in a composite data structure have dependencies and there exists relations/invariances on these variables.

#### Contents

- Execution model for multithreaded program

- Four classes of race detection techniques

- For each class,

- bug example

- bug conditions

- techniques for checking conditions

Implications for better race detections

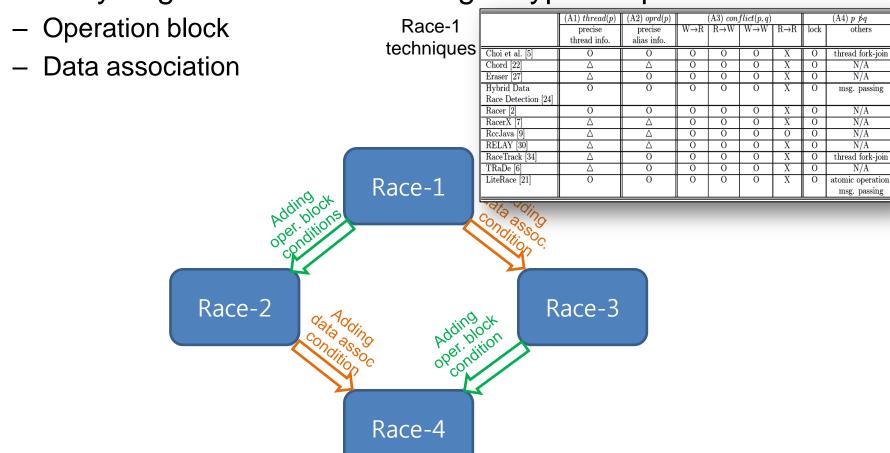

### Race-1: Data-race

(1/6)

In parallelization,

A sufficient condition for safe parallelization:

```

MemoryRead(B<sub>1</sub>) \cap MemoryWrite(B<sub>2</sub>) = \emptyset and MemoryWrite(B<sub>1</sub>) \cap MemoryRead(B<sub>2</sub>) = \emptyset

```

- In "What are race conditions?" [R. H. Netzer et al., LOPLAS 1992],

a data race <a, b> over an execution exists if and only if

- (1) a data conflict exists in a program between a and b,

- (2) no temporal ordering between a and b.

#### Race-1: Data-race

(2/6)

- In [Savage et al., SOSP 1997],

a data race occurs when there exists two operations

- (1) executed by two concurrent threads,

- (2) access a shared variable

- (3) at least one access is write,

- (4) no explicit mechanism to coordinate their execution order

- Buggy program code

```

class BankAccount_A {

int balance;

// balance should be non-negative

void withdraw(int x) {

1: if (balance >= x) {

2: balance = balance - x;}}

... }

```

- Error scenario

```

[ balance = 10 ]

--t1: withdraw(10)--

1:if(balance>= 10)

1:if(balance>= 10) p

2:balance = 0 - 10;

The invariant is violated:

balance becomes -10.

```

- A target program P has a race-1 bug if there is an execution  $\sigma$  such that  $\sigma$  has two operations p and q that satisfy the following conditions:

- (A1)  $thread(p) \neq thread(q)$

- (A2)  $oprd(p) \cap oprd(q) \neq \emptyset$

- (A3) conflict(optr(p), optr(q))

- (A4)  $p \not\triangleright q \land q \not\triangleright p$

p and q are commutable?

### Race-1: Data-race

(4/6)

#### Race-1 Detection Techniques

|                            | (A1)                       | (A2)                     | (A3) |                            |     |     | (A4)                                                              |

|----------------------------|----------------------------|--------------------------|------|----------------------------|-----|-----|-------------------------------------------------------------------|

|                            | thread(p)                  | $oprd(p) \cap$           | conf | conflict(optr(p), optr(q)) |     |     | $p \not\triangleright q$                                          |

|                            | $\neq thread(q)$           | $oprd(q) \neq \emptyset$ | W-R  | R-W                        | W-W | R-R |                                                                   |

| Choi et al.                | concrete<br>thread id.     | concrete<br>mem. addr.   | 0    | 0                          | 0   | Х   | tracking lock acq/rel,<br>thread fork/join                        |

| Eraser                     | check shared or non-shared | concrete<br>mem. addr.   | 0    | 0                          | 0   | Х   | tracking lock acq/rel                                             |

| Hybrid data race detection | concrete<br>thread id.     | concrete<br>mem. addr.   | 0    | 0                          | 0   | Х   | tracking lock acq/rel,<br>message send/receive                    |

| Racer                      | concrete<br>thread id.     | concrete<br>mem. addr.   | 0    | 0                          | 0   | Х   | tracking lock acq/rel                                             |

| RaceTrack                  | check shared or non-shared | concrete<br>mem. addr.   | 0    | 0                          | 0   | X   | tracking lock acq/rel, thread fork/join                           |

| TRaDe                      | check shared or non-shared | concrete<br>mem. addr.   | 0    | 0                          | 0   | Х   | tracking lock acq/rel                                             |

| LiteRace                   | concrete<br>thread id.     | concrete<br>mem. addr.   | 0    | 0                          | 0   | Х   | tracking lock acq/rel,<br>message passing,<br>atomic instructions |

| Chord                      | static approx.             | static alias<br>analysis | 0    | 0                          | 0   | Х   | tracking lock acq/rel                                             |

| RacerX                     | static approx.             | static alias<br>analysis | 0    | 0                          | 0   | Х   | tracking lock acq/rel                                             |

| RELAY                      | static approx.             | static alias<br>analysis | 0    | 0                          | 0   | Х   | tracking lock acq/rel                                             |

| RccJava                    | static approx.             | static alias<br>analysis | 0    | 0                          | 0   | 0   | tracking lock acq/rel                                             |

16

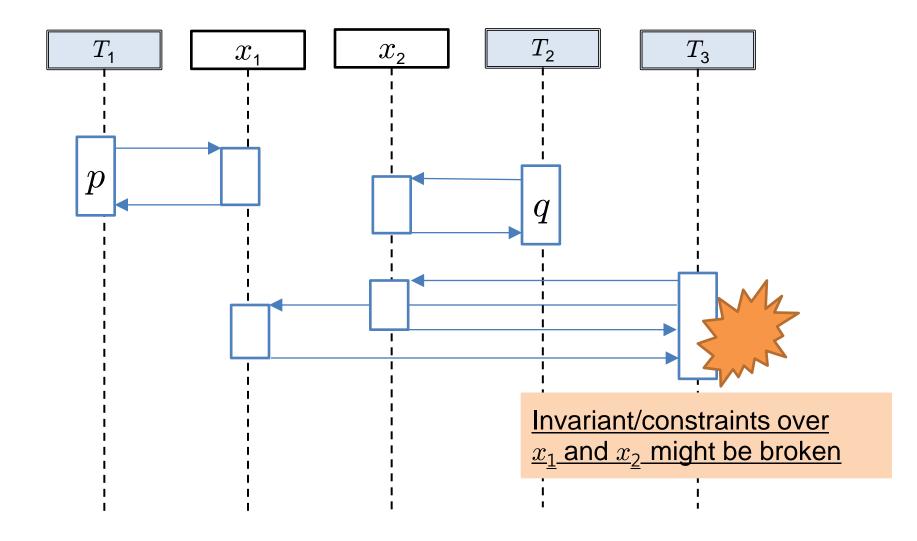

Limitations – false positive

(6/6)

Limitations – false negative

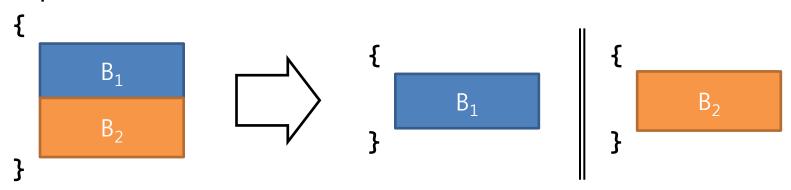

# Race-2: Atomic Block Violation (1/5)

Race-2 techniques check whether or not an operation block can interfere with another thread.

In [Savage et al., SOSP 1997], From a previous slide for race-1

a data race occurs when there exists two operations

(1) executed by two concurrent threads,

(2) access a shared variable

(3) at least one access is write,

(4) no explicit mechanism to coordinate their execution order

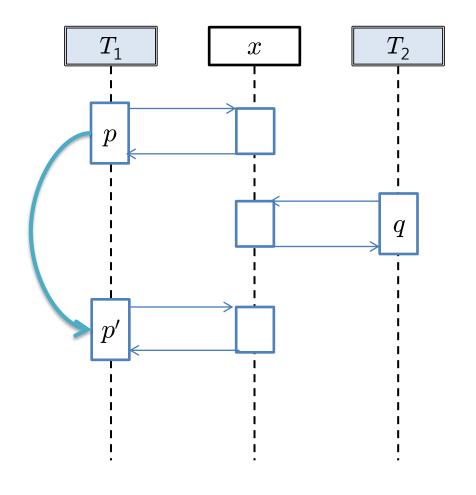

# Race-2: Atomic Block Violation (2/5)

• A target program P has a *race-2 bug* if there is an execution  $\sigma$  such that  $\sigma$  has three operations p, p', and q that satisfy the following conditions:

| (B1)    | $thread(p) \neq thread(q)$                    |

|---------|-----------------------------------------------|

| (B2)    | $oprd(p) \cap oprd(q) \neq \emptyset$         |

| (B3)    | conflict(optr(p), optr(q))                    |

| $(B_4)$ | $\exists \ b_i \in B_{op}.(\ (p,p') \in b_i)$ |

| (B5)    | $oprd(p) \cap oprd(p') \neq \emptyset$        |

| (B6)    | conflict(optr(p), optr(p'))                   |

| (B7)    | $oprd(p') \cap oprd(q) \neq \emptyset$        |

| (B8)    | conflict(optr(p'), optr(q))                   |

| (B9)    | $q  ot p \land p'  ot p q$                    |

### Race-2: Atomic Block Violation (3/5)

Race-2 bug example:

```

- Buggy program code

class BankAccount B {

Lock m:

int balance;

// balance should be non-negative

// balance should be synchronized by m

int getBalance() {

int tmp;

1: lock(m);

2: tmp = balance;

3: unlock (m);

4: return tmp; }

void withdraw(int x) {

/*@atomic region begins*/

if (getBalance() >= x) {

12: lock(m);

13:

balance = balance - x ;

14:

unlock(m); }

/*@atomic region ends*/

```

- Race-2 error scenario

```

[ balance = 10 ]

--t1: withdraw(10)-- :--t2: withdraw(10)--

operation block b<sub>i</sub>

11:if(getBalance()>=10)

\Rightarrow 1:lock (m);

2:tmp = balance; p

3:unlock(m);

4:return tmp;

12: lock(m);

13: balance=10-10; q

14: unlock(m);

12: lock(m);

13: balance=0-10;

14: unlock(m);

The invariant is violated:

balance becomes -10.

```

# Race-2: Atomic Block Violation (4/5)

#### Race-2 Detection Techniques

|                       | (B1)                   | (B2,<br>B4,B7)         | (B6) $conflict(optr(p), optr(q))$ |      |                      |                | (B3, B8) $conflict(optr(p), optr(q))$ |         |               |                | (B9)                                     |

|-----------------------|------------------------|------------------------|-----------------------------------|------|----------------------|----------------|---------------------------------------|---------|---------------|----------------|------------------------------------------|

|                       | thread()               | oprd()                 | where<br>W-R                      | R-W  | $(p) \neq thr$ $W-W$ | ·ead(q)<br>R-R | where<br>W-R                          | thread( | (p) = thr W-W | read(q)<br>R-R | <b>&gt;</b>                              |

|                       |                        |                        | VV-P                              | K-VV | VV-VV                | K-K            | VV-K                                  | K-VV    | VV-VV         | K-K            |                                          |

| Atomic-Aid            | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | Cond.                | X              | 0                                     | 0       | 0             | 0              | tracking lock/unlock                     |

| AtomRace              | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | Cond.                | Х              | 0                                     | 0       | 0             | 0              | tracking lock/unlock                     |

| AVIO                  | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | Cond.                | Х              | 0                                     | 0       | 0             | 0              | total<br>execution order                 |

| Block-based algorithm | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | Cond.                | Х              | 0                                     | 0       | 0             | 0              | tracking lock/unlock,<br>message passing |

| Commit-node           | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | 0                    | Х              | 0                                     | 0       | 0             | 0              | tracking lock/unlock<br>message passing  |

| HAVE                  | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | 0                    | X              | 0                                     | 0       | 0             | 0              | tracking lock/unlock message passing.    |

| Kivati                | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | Cond.                | Х              | 0                                     | 0       | 0             | 0              | total<br>execution order                 |

| SVD                   | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | 0                    | 0              | X                                     | X       | 0             | 0              | total<br>execution order                 |

| PENELOPE              | concrete thread id.    | concrete<br>mem. addr. | 0                                 | 0    | 0                    | Х              | 0                                     | 0       | 0             | 0              | tracking lock/unlock                     |

| Velodrome             | concrete<br>thread id. | concrete<br>mem. addr. | 0                                 | 0    | 0                    | Х              | 0                                     | 0       | 0             | 0              | tracking lock/unlcok,<br>message passing |

| Atomizer              | static<br>apprx.       | alias<br>analysis      | 0                                 | 0    | 0                    | 0              | 0                                     | 0       | 0             | 0              | tracking lock/unlock                     |

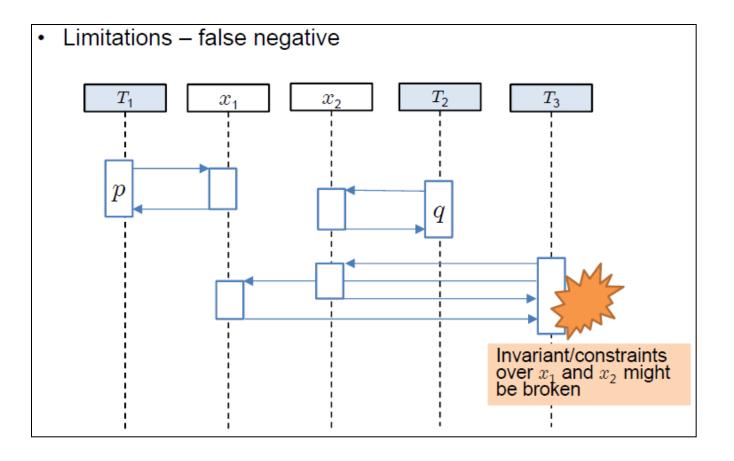

## Race-2: Atomic Block Violation (5/5)

Limitation: false-negative

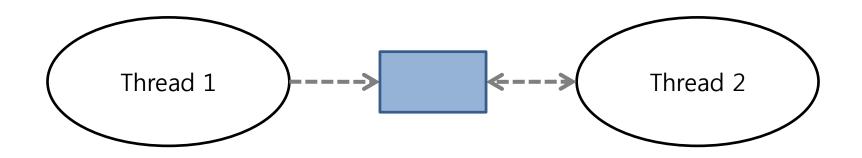

# Race-3: Data Assoc. Violation (1/4)

- A unit of data can be located in two or more distinct variables.

- Race-3 detection techniques look for <u>inconsistent updates of associated</u> variables. [K. Havelund VVEIS03, S. Lu SOSP07, F. Tip ICSE08]

In [Savage et al., SOSP 1997],

a data race occurs when there exists two operations

(1) executed by two concurrent threads,

(2) access a shared variable

(3) at least one access is write,

(4) no explicit mechanism to coordinate their execution order

### Race-3: Data Assoc. Violation (2/4)

Race-3 bug condition:

(C1)

$$thread(p) \neq thread(q)$$

$$(C2) \qquad \exists v_1, v_2 \in V_S. (v_1 \in oprd(p) \land v_2 \in oprd(q) \land (v_1, v_2) \in A_{data})$$

(C3)

$$conflict(optr(p), optr(q))$$

$$(C4)$$

$p \not\triangleright q \land q \not\triangleright p$

# Race-3: Data Assoc. Violation

#### Example

```

class BankAccount C {

int

balance :

int debt:

/* Invariant:

(balance == 0 \land debt == 0) \lor

(debt > 0 \rightarrow balance == 0) \lor

(balance > 0 \rightarrow debt == 0) */

ightharpoonup (balance, debt) \in A_{data} \wedge

(debt, balance) \in A_{data}

Lock m_balance ;

Lock m_debt ;

```

```

[ balance=0, debt=10 ]

--t2: withdraw(5)--

--t1: deposit(20)--

21:if(getBalance()==0)

11:lock(m debt);

12:if(0 < 10 \&\& 10 <=20)

13: tmp = 20-10;

14:dept=0;

15:unlock(m debt);

16:lock(m balance);

22:lock(m debt);

17:balance = 10;

23:debt = 0+5; q

The invariant is violated:

balance is 10 and debt is 5

```

## Race-3: Data Assoc. Violation (4/4)

#### Race-3 detection techniques

|                            | (C1)  thread()      | <b>(</b>                                                     | (C3)            | (C4)           |                              |                     |                         |

|----------------------------|---------------------|--------------------------------------------------------------|-----------------|----------------|------------------------------|---------------------|-------------------------|

|                            | inreau()            | Туре                                                         | transi-<br>tive | symm-<br>etric | Source                       | conjuci()           | <b>⋫</b>                |

| MultiRace                  | Concrete thread id. | $[a_1, a_2,, a_n]$                                           | 0               | 0              | User annotation              | W-R,<br>R-W,<br>W-W | tracking<br>lock/unlock |

| MUVI-Eraser                | Heuristics          | $<\!(a_1,t_1),(a_2,t_2)\!>$ where $t_1,t_2\in\{rd,wr,rd\≀\}$ | Х               | Х              | Inferring<br>from executions | W-R,<br>R-W,<br>W-W | tracking<br>lock/unlock |

| Object data race detection | Static apprx.       | $\{a_1, a_2,, a_n\}$                                         | 0               | 0              | User annotation              | W-R,<br>R-W,<br>W-W | tracking<br>lock/unlock |

Race-4

2011-06-27

Race-4 techniques utilize both operation block and data association together to reduce false positives and false negatives.

In [Savage et al., SOSP 1997],

From a previous slide for Race-1

a data race occurs when there exists two operations

- (1) executed by two concurrent threads,

- (2) access a shared variable

- (3) at least one access is write,

- (4) no explicit mechanism to coordinate their execution order

Hong, Shin @ PSWLAB

/ 33

Race-4

(2/4)

Race-4 bug conditions:

| 3       |                                                               | Race-B condition        | ns                               |

|---------|---------------------------------------------------------------|-------------------------|----------------------------------|

| (D1)    | $thread(p) \neq thread(q)$                                    | Race-C condition        | ns                               |

| (D2)    | $\exists v_{1}, v_{2} \in V_{S}.(v_{1} \in oprd(p))$          | $\land v_2 \in oprd(q)$ | $\land (v_1, v_2) \in A_{data})$ |

| (D3)    | conflict(optr(p), optr(q))                                    |                         |                                  |

| $(D_4)$ | $\exists v_3, v_4 \in V_S$ . $(v_3 \in oprd(p'))$             | $\land v_4 \in oprd(q)$ | $\land (v_3, v_4) \in A_{data})$ |

| (D5)    | conflict(optr(p'), optr(q))                                   |                         |                                  |

| (D6)    | $\exists \; b_i \in B_{op}$ .( $(p,p') \in b_i$ )             |                         |                                  |

| (D7)    | $\exists v_{5},v_{6}\!\in V_{S}$ . ( $v_{5}\!\!\in\!oprd(p')$ | $\land v_6 \in oprd(q)$ | $\land (v_5, v_6) \in A_{data})$ |

| (D8)    | conflict(optr(p), optr(p'))                                   |                         |                                  |

| (D9)    | $q \not\triangleright p \wedge p' \not\triangleright q$       |                         |                                  |

Race-4

(3/4)

#### - Buggy program

```

class BankAccount D {

Lock m;

int balance, debt;

/*(balance, debt)\in A_{data}

(debt, balance) \in A_{data} * /

int getBalance(int x) {

int tmp;

1: lock(m);

2: tmp = balance;

3: unlock(m);

4: return tmp; }

int withdraw(int x) {

11: if (getBalance() == 0) { b_1

12: lock(m);

13: debt = debt + x;

14: unlock(m);}}

int deposit(int x) {

21: lock(m);

22: if (balance == 0) {

23: if (x > debt) {

balance = x - debt;

24:

25:

debt = 0; }

26:

27:

unlock (m); }

```

#### - Error execution scenario

```

[balance=0, debt=10]

--t2: deposit(20)--

--t1: withdraw(5)--

11:if(getBalance()== 0)

\downarrow 1: lock (m);

2: tmp = 0;

\boldsymbol{\zeta}

3: unlock(m);

21:lock(m);

22:if(0 == 0)

23:if(20 > 10);

24:balance= 20-10; q

25:debt = 0;

26: ...

27:unlock(m);

12:lock(m);

13: debt = debt + 5; \langle p' \rangle

14: unlock(m);

The invariant is violated:

balance is 10 and debt is 15

```

Race-4 (4/4)

#### Race-4 detection techniques

|                            | (D1)  thread()      | (D2, D4, $A_{data}$                                                      |                 | (D3,D5)<br>conflict()<br>where | (D6,D8)<br>conflict()<br>where | (D9)<br>⊭                    |                             |

|----------------------------|---------------------|--------------------------------------------------------------------------|-----------------|--------------------------------|--------------------------------|------------------------------|-----------------------------|

|                            | on caa(y            | Туре                                                                     | transi-<br>tive | symm-<br>etric                 | $thread(p)$ $\neq thread(q)$   | $thread(p)$ $\neq thread(q)$ | P                           |

| Atomic-Set serializability | Concrete thread id. | < a <sub>1</sub> , a <sub>2</sub> >                                      | 0               | 0                              | W-R,<br>R-W,<br>W-W            | W-R,<br>R-W,<br>W-W,<br>R-R  | total<br>execution<br>order |

| ColorSafe                  | Concrete thread id. | < a <sub>1</sub> , a <sub>2</sub> >                                      | 0               | 0                              | W-R,<br>R-W,<br>W-W            | W-R,<br>R-W,<br>W-W,<br>R-R  | total<br>execution<br>order |

| Method-<br>consistency     | Static apprx.       | $<\!(a_1,t_1),(a_2,t_2)\!>$ where $t_1,t_2\in\{read,update\}$            | 0               | 0                              | W-R,<br>R-W,<br>W-W,<br>R-R    | W-R,<br>R-W,<br>W-W,<br>R-R  | tracking<br>lock/unlock     |

| MUVI-AVIO                  | Concrete thread id. | $<\!(a_1,t_1),(a_2,t_2)\!>$ where $t_1,t_2\in\{rd,wr,rd\≀\}$             | Х               | Х                              | W-R,<br>R-W,<br>W-W(cond),     | W-R,<br>R-W,<br>W-W,<br>R-R  | total<br>execution<br>order |

| View-<br>consistency       | Concrete thread id. | <(a <sub>1</sub> , t <sub>1</sub> ), (a <sub>2</sub> , t <sub>2</sub> )> | 0               | 0                              | W-R,<br>R-W,<br>W-W,<br>R-R    | W-R,<br>R-W,<br>W-W,<br>R-R  | tracking<br>lock/unlock     |

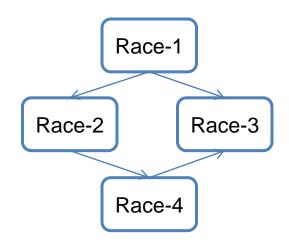

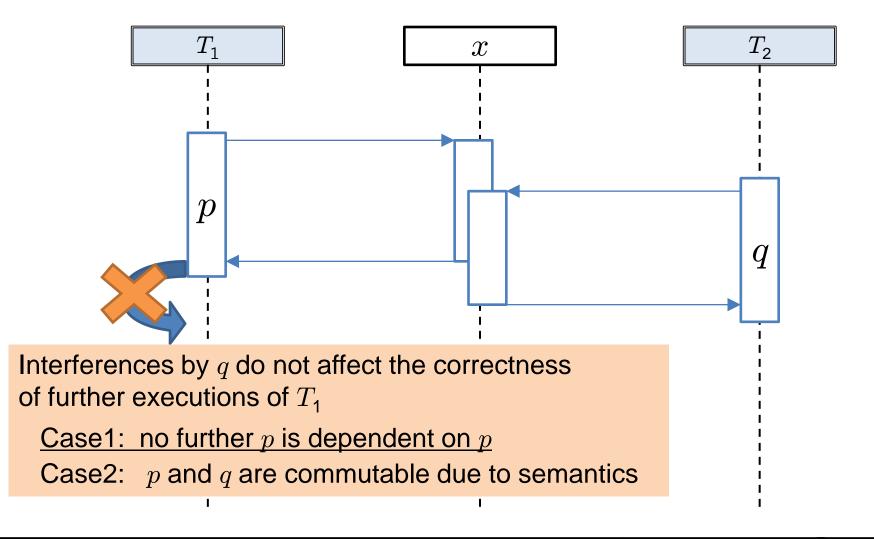

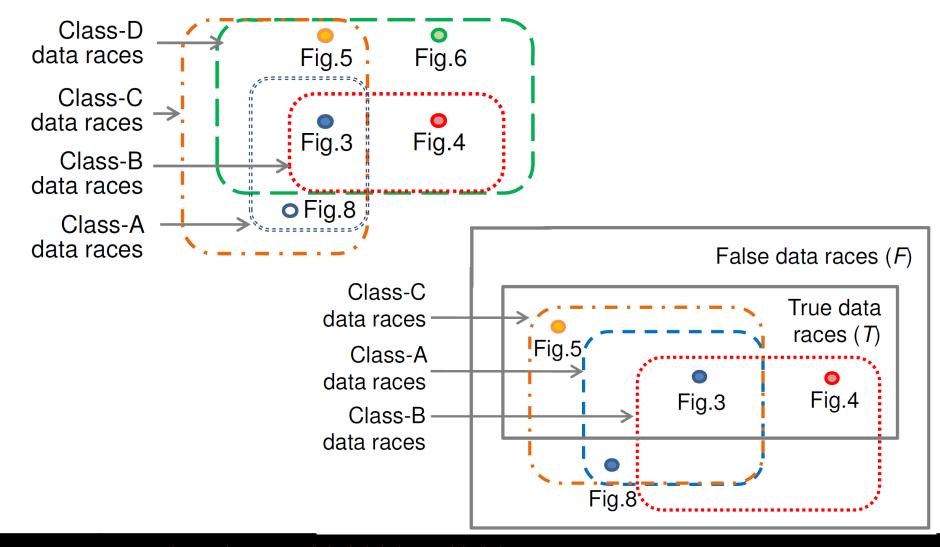

### Implications to Better Race Detection (1/2)

Relations in four class of race detections

### Implications to Better Race Detection (2/2)

- Static analyses can be applied for much precise race detections

- Only few work use static analyses for inferring/checking operation block and data associations

**Theorem 1.** Let  $G^{du} = (G, \Sigma, D, U)$  be a def/use graph with G = (N, E), and let  $u, v \in N$ . If u is semantically dependent on v and this semantic dependence is finitely demonstrated, then u is syntactically dependent on v.

Theorem 1 is significant because it shows that, given appropriate definitions of control and data dependence, syntactic dependence is a necessary condition for (finitely demonstrated) semantic dependence. Thus, the theorem provides justification for algorithms that use syntactic dependence to approximate semantic dependence. We refer to this desirable relationship between syntactic and semantic dependence as the "syntactic–semantic relationship".

M. J. Harrold, G. Rothermel, and S. Sinha. "Computation of Interprocedural Control Dependence" Proceedings of the ACM International Symposium on Software Testing and Analysis, March 1998.

/ 33